Lithography

Lithography

大量内容转载自 Litho+ wiki

Photoresist

定义

光刻胶是一大类具有光敏化学作用的高分子聚合物材料,又称为光阻、抗蚀剂等。光可以是 UV 波段的 i-line (365nm)、g-line (436nm)、DUV、EUV,也可以是电子束(E-beam)、X-ray、离子束,甚至是同步辐射光源等。

分类

根据化学作用机理不同,光刻胶可以分为正胶和负胶。

正胶:从光敏化学反应解释,正型光刻胶是长链聚合物分子因光照链解(chain secession)。从图形上来说,光照区域的光刻胶被显影掉,未被光照区域的光刻胶保留,为正胶(positive photoresist)。

负胶:聚合物因光照交联(cross linking),变得不溶于显影液,为负胶。从图形上来说,光刻过程中被的光照的区域在显影过程中留下来,未被光照区域被显影掉,从而在基底材料上留下与掩膜板相反的图形,为负胶(negative photoresist)。

相对负胶而言,正胶主要优点:高分辨率,高对比度;使用暗场掩模减少了曝光图形的缺陷率,因为掩模大部分区域都是不透光的;使用水溶性显影液,去胶容易。

光刻胶的选择

选择光刻胶需要综合考虑:

-

掩模板制作成本:光刻胶的选择与设计的图形密切相关,目的是降低掩膜板的制作成本

-

工艺匹配度:在 lift-off 工艺中,需要 undercut 结构,紫外光刻负胶更容易获得 undercut 结构,电子束光刻中正胶更容易获得 undercut 结构

-

光刻胶的使用成本

剥离工艺 (lift-off)

定义

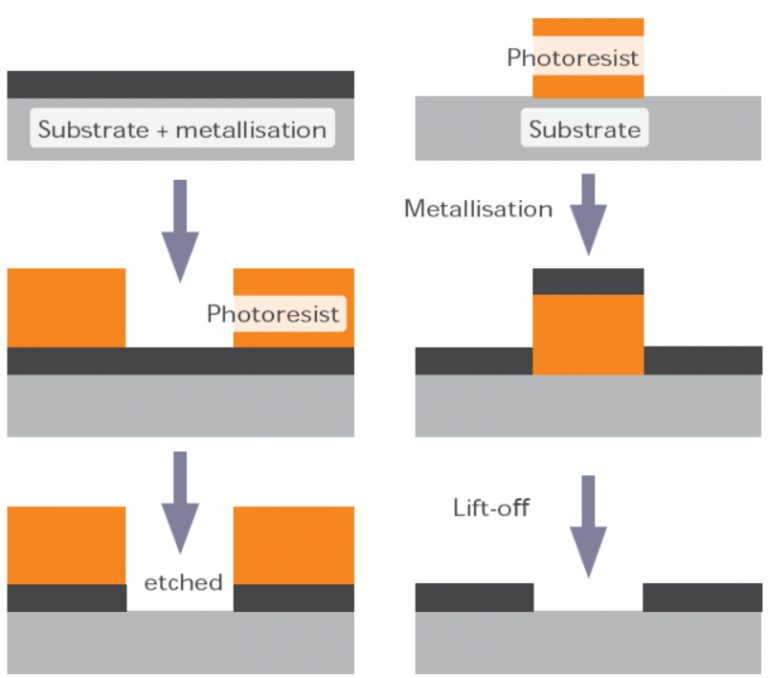

剥离工艺(lift-off)是一种图形转移手段,简单易行;是制作电极的基础手段。

在衬底上用光刻工艺获得图案化的光刻胶结构或者金属硬掩膜等掩膜(shadow mask),利用镀膜工艺在掩膜上镀上目标涂层,再利用去胶液(又称剥离液)溶解光刻胶或者机械去除硬掩膜的方式获得与图案一致的目标图形结构,我们称之为剥离工艺。

影响工艺因素

- 光刻胶厚度

由定义可知,光刻胶在该工艺中的作用有两点:提供图案;提供高度差,让光刻胶上的薄膜层与衬底上沉积的薄膜层断开,使得光刻胶在去胶液中溶解时,上层金属更易脱离。所以,光刻胶的厚度很关键,通常经验值为:光刻胶厚度/被剥离金属厚度 ≥ 3。但是光刻胶的厚度会影响其分辨率,所以 lift-off 工艺不适用于特别厚的金属剥离。

- 光刻胶种类

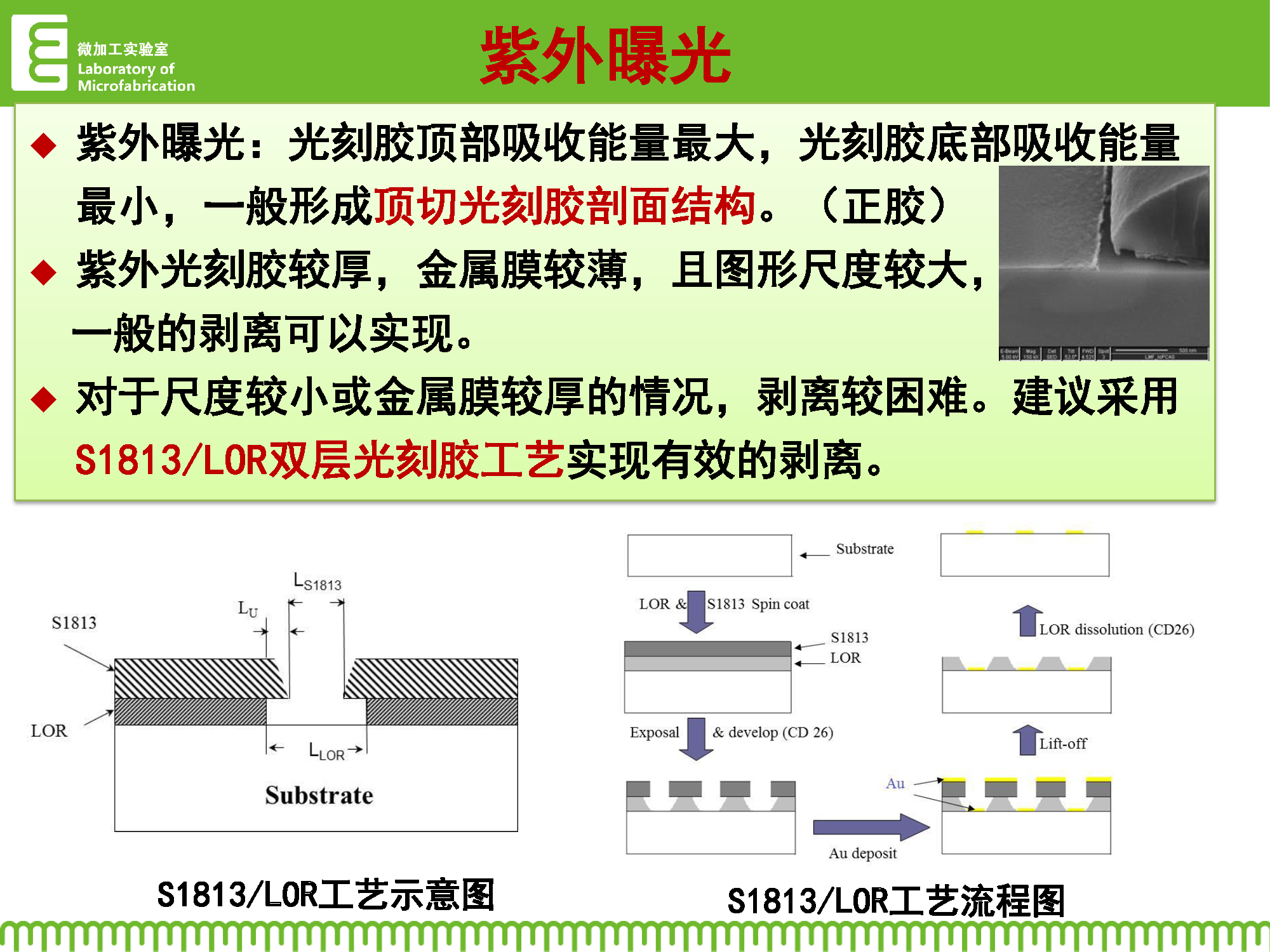

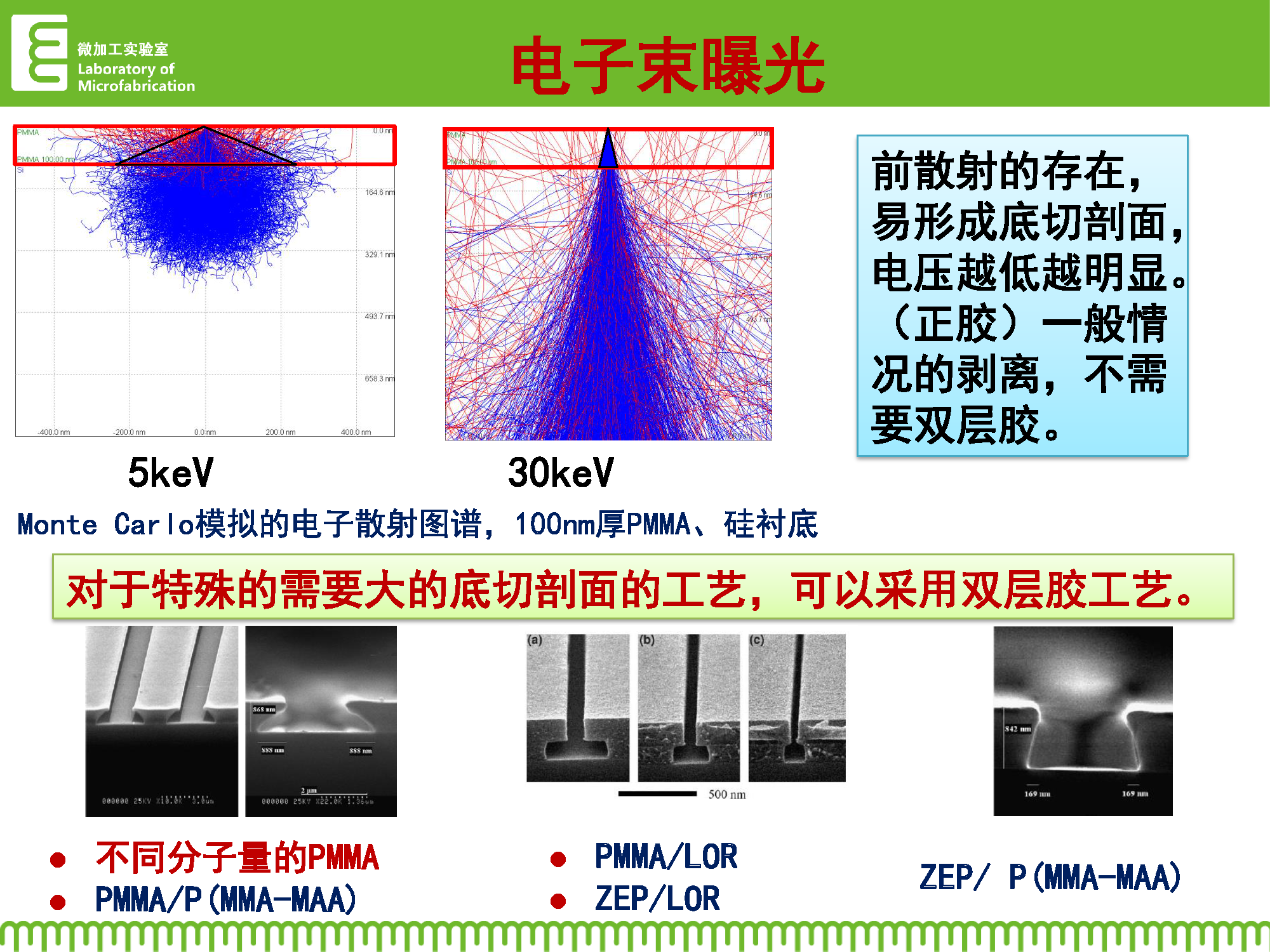

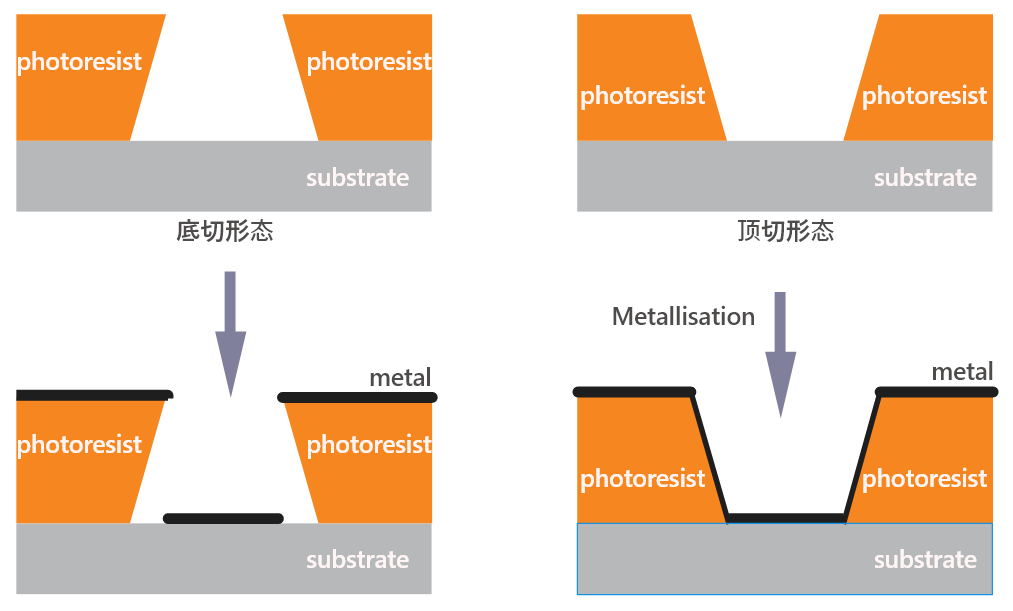

lift-off 工艺在紫外光刻和电子束光刻中都很常见,但是两者在光刻胶选择上有着较大差异。引入一类新概念,光刻胶的刻蚀形态:底切(under cut)和顶切(top cut),具体形态如下图所示。可直观看出光刻胶的形态对于 lift-off 成功与否有着直接关系,所以需要 under cut 结构。对于紫外光刻(含激光直写),其机理决定了,负胶(如AR-N 4340)相比于正胶更容易获得 under cut 形态,图形反转胶(AR-U 4000)的负胶工艺可以获得完美的 under cut 结构。而电子束胶光刻中,电子与光刻胶作用过程中存在散射,正胶(如PMMA)相比于负胶更容易获得 under cut 结构。

- 双层胶工艺

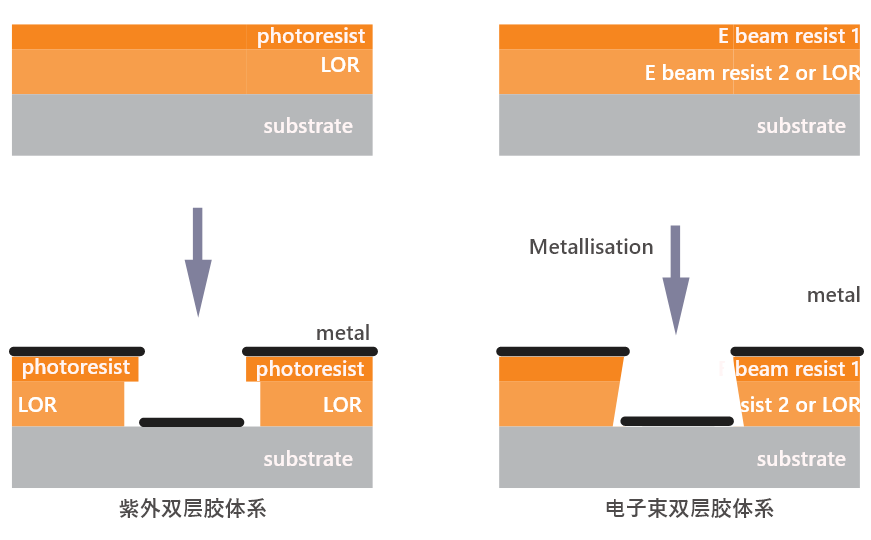

通过双层胶 lift-off 方案来控制形成 under cut 结构。

紫外胶和电子束胶的原理和方案上有一些区别:

-

紫外胶,将不含光敏的剥离胶(LOL,LOR,如AR-BR 5400)置于紫外正胶或者负胶底层,利用上层胶的光刻胶经曝光显影后开出窗口,底层胶在显影液中继续腐蚀,并产生横向拓展,形成 under cut 结构,横向拓展的深度与显影液的碱当量以及显影时间呈正相关。

-

电子束胶,通常两种不同灵敏度的正胶,将高灵敏度的胶置于底层,低灵敏度的胶置于上层,在曝光、显影过程中高灵敏度胶相比于低灵敏度胶空腔结构会更宽,获得 under cut。也可将 LOR 胶置于电子束胶下层,利用两次显影工艺获得 under cut 结构。

体系结构示意图如上,双层胶体系中,底层胶的厚度是被剥离金属层厚度1.25倍以上。上层胶来控制线宽。横向拓展深度不易过深,否则容易在显影后干燥时,由于液体表面张力导致胶体坍塌。

PS:文章 lift-off 介绍了更多 lift-off 工艺制备金属电极时的影响因素。

流片 (Tape Out)

定义

流片,指像流水线一样通过一系列工艺步骤制造芯片。在集成电路设计领域,“流片”指的是“试生产”。设计结束后,先生产几片几十片,用于测试。测试通过,再开始大规模生产。

为什么是 Tape Out

Tape Out 是指芯片完成了设计,将设计数据交给 fab 开始生产,很多年前,完成的设计数据都是写到磁带里传给 fab。设计团队将数据写入磁带叫 tape in,fab 读取磁带的数据叫 tape out,现在科技发展了已经不用磁带了,但这个词还是沿用了下来。

Wafer Out

wafer Out 是指 wafer 在 fab 完成了生产,设计的集成电路已经制造在硅基上了,晶圆表面上所有芯片工序及磊晶过程完全完成,离开工厂,下一步就要进行封装测试了。

Classification of semiconductor companies

芯片有设计和生产两部分,Fabless 设计,Foundry 生产,IDM 通吃。

Fabless

Fabless 企业只从事芯片设计与销售,不从事生产,因此又被称为“无厂化企业”。芯片开发设计所需成本较低,因此公司很多,比如手机厂商华为、苹果和小米,还有高通和联发科,都属于 Fabless。其中,开发设计也分为前端和后端;前端相对于后端投入成本更低,设计周期更快,因此很多小公司只做前端设计,后端则交给专业的后端公司进行设计实现。

IDM

IDM 指既能够自行设计、也能够自行生产的芯片厂商,如三星和英特尔。目前受到美国打压,华为也正在增强自身的生产能力。

Foundry

Foundry 是可以完成芯片制造,但是没有设计能力的厂商,也称“代工厂”。台积电TSMC 就是典型的 Foundry,帮助 Fabless 完成生产。